VDIERVA

teraste

www.terasic.com

Copyright © 2003-2016 Terasic Inc. All Rights Reserved.

| CHAPTER 1    | DE5A-NET OPENCL                  |   |

|--------------|----------------------------------|---|

| 1.1 System R | LEQUIREMENT                      |   |

| 1.2 OPENCL A | ARCHITECTURE                     |   |

| CHAPTER 2    | OPENCL FOR WINDOWS               | 5 |

| 2.1 Softwar  | E INSTALLATION                   | 5 |

| 2.2 OPENCL I | LICENSE INSTALLATION             | 7 |

| 2.3 CONFIGUE | RE                               |   |

| 2.4 BOARD SE | ETUP                             |   |

| 2.5 OPENCL H | ENVIRONMENT VERIFY AND FLASH CVP |   |

| 2.6 COMPILE  | AND TEST OPENCL PROJECT          |   |

| CHAPTER 3    | OPENCL FOR LINUX                 |   |

| 3.1 SOFTWAR  | E INSTALLATION                   |   |

|              | LICENSE INSTALLATION             |   |

| 3.3 CONFIGUE | RE                               |   |

| 3.4 BOARD SE | ETUP                             |   |

| 3.5 OPENCL I | ENVIRONMENT VERIFY AND FLASH CVP |   |

| 3.6 COMPILE  | AND TEST OPENCL PROJECT          |   |

## Chapter 1

# DE5a-Net OpenCL

DE5a-Net, an unparalleled and powerful platform for high-speed computation, is now officially also an Altera certified board for Intel's Preferred Board Partner Program for OpenCL. It supports both 64-bit Windows and Linux. This document will introduce you how to setup OpenCL development environment for DE5a-Net board, and how to compile and execute the example projects for DE5a-Net. Note that OpenCL coding instruction is not in the scope of this document, but the user can refer to Altera SDK for OpenCL Programming Guide for more details.

https://www.altera.com/en\_US/pdfs/literature/hb/opencl-sdk/aocl\_programming\_guide.pdf

### **1.1 System Requirement**

The following items are required to set up OpenCL for DE5a-Net board:

- DE5a-Net Board with two 4GB DDR3-SODIMM installed on two DDR3-SODIMM port.

- A Host PC with

- USB Host Port

- One PCI Express x8/x16 slot with 12V power pin

- 32GB memory is recommended, 24GB is minimal

- 2x3 pin 12V Power for DE5a-Net (optional)

- An USB Cable(type A to mini-B)

- 64-bit Windows7/10 or Linux(Redhat 6.5/CentOS 7.0) Installed

- Intel Quartus Prime Pro Edition 16.1 Installed, licensed is required

- Intel FPGA SDK for OpenCL 16.1 Installed, license is required

- DE5a-Net OpenCL BSP 16.1 Installed

- Visual Studio 2012 C/C++ installed for Windows7/10

- GNU development tools for Linux

#### Note:

- 1. Intel FPGA OpenCL only supports 64-bit OS and x86 architecture.

- 2. We strongly recommend setting the PCIe speed to **Gen3x8** in your PC BIOS for good performance.

erasic DE5a-Net OpenCL

www.terasic.com March 29, 2017

### **1.2 OpenCL Architecture**

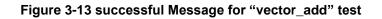

An OpenCL project is composed of both OpenCL Kernel and Host Program as shown in **Figure 1-1**. OpenCL kernel is compiled with Intel FPGA OpenCL compiler provided by the Altera OpenCL SDK. The Host Program is compiled by Visual Studio C/C++ in Windows or GCC on Linux.

Figure 1-1 Intel FPGA OpenCL Architecture

## Chapter 2

# **OpenCL for Windows**

This chapter describes how to set up DE5a-Net OpenCL development environment on 64-bit Windows, and how to compile and test the OpenCL examples for DE5a-Net. For more details about Intel FPGA OpenCL started guide, please refer to:

https://www.altera.com/en\_US/pdfs/literature/hb/opencl-sdk/aocl\_getting\_started.pdf

### **2.1 Software Installation**

This section describes where to get the required softwares for OpenCL.

### Quartus II and OpenCL SDK

Intel Quartus Prime Pro Edition 16.1 and Intel FPGA SDK for OpenCL 16.1 can be download from the web site:

http://dl.altera.com/opencl/16.1/?edition=standard

For Quartus II installation, please make sure that the Arria 10 device is included.

open the link and select the **Windows SDK** table as **Figure 2-1**shows.

#### Download Center

Get the complete suite of Intel® design tools

|                       |                              | 7 myAltera Account Help                                                            | 🗹 Terms and Conditio |

|-----------------------|------------------------------|------------------------------------------------------------------------------------|----------------------|

| Design Software       |                              |                                                                                    |                      |

| Embedded Software     | Intel FPGA SDK for           | OpenCL                                                                             |                      |

| Archives              | Release date: November, 2016 |                                                                                    |                      |

| Licensing             | Latest Release: v16.1        | 1. Quartus Prime Standard Edition                                                  |                      |

| Programming Software  | Select release: 16.1 🔻       | 2. Quartus Prime Pro Edition<br>3. Intel FPGA SDK for OpenCL                       |                      |

| Drivers               |                              | 4. Arria 10 Part 1                                                                 |                      |

| Board System Design   | Download Method 🍞 🖲 Akamai I | 5. Arria 10 Part 2 <sup>wnload</sup>                                               |                      |

| Board Layout and Test |                              | 6. Arria 10 Part 3                                                                 |                      |

| Legacy Software       | Windows SDK Linux SD         | 7. Arria V                                                                         |                      |

|                       |                              | 8. Cyclone V                                                                       |                      |

|                       | Download and install inst    | S. Studix V                                                                        |                      |

|                       | Read Intel FPGA SDK for Ope  | ence octants started same                                                          |                      |

|                       |                              | CL (includes Quartus Prime software and devices) 🕖<br>BD1058D329D4860F9EBA184719BF |                      |

|                       | Download                     |                                                                                    |                      |

#### Figure 2-1 OpenCL Windows SDK Files

### ■ Visual Studio 2012

If developers don't have Visual studio C/C++ 2012, they can use the trial version of Visual Studio 2012 Express. The software can be downloaded from the web site:

http://www.microsoft.com/en-us/download/details.aspx?id=34673

### ■ DE5a-Net OpenCL BSP (Board Support Package)

After Quartus II and OpenCL SDK are installed, download the DE5ANET\_E1\_OpenCL\_BSP \_16.1.zip DE5a-Net windows BSP for Intel FPGA OpenCL 16.1 from the web:

http://de5a-net.terasic.com/cd

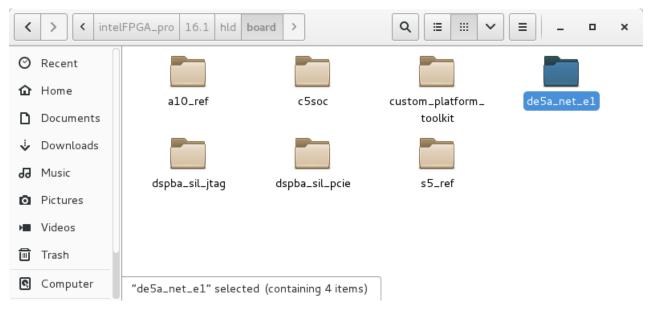

Then, decompress DE5ANET\_E1\_OpenCL\_BSP\_16.1.zip to the "de5a\_net\_e1" folder under the folder "C:\intelFPGA\_pro\16.1\hld\board", as shown in Figure 2-2, where assumed Quartus II is installed on the folder "C:\ intelFPGA\_pro \16.1".

|                  |       | ► Local Disk (C:) ► intelFPGA_pro ► |                 | ✓ <sup>4</sup> → Sean | ch board | - |   |   |

|------------------|-------|-------------------------------------|-----------------|-----------------------|----------|---|---|---|

| )rganize 🔻 Inclu | de in | library ▼ Share with ▼ New fol      | der             |                       |          | : | • | ( |

| Favorites        | -     | Name                                | Date modified   | Туре                  | Size     |   |   |   |

| 🧮 Desktop        |       | 🐌 a10_ref                           | 2017/2/22 11:31 | File folder           |          |   |   |   |

| 🐌 Downloads      | Ξ     | J c5soc                             | 2017/2/22 11:32 | File folder           |          |   |   |   |

| 📃 Recent Places  |       | custom platform_toolkit             | 2017/2/22 11:32 | File folder           |          |   |   |   |

|                  |       | 🕕 de5a_net_e1                       | 2017/3/10 16:08 | File folder           |          |   |   |   |

| 🗃 Libraries      |       | 📗 dspba_sil_jtag                    | 2017/2/22 11:32 | File folder           |          |   |   |   |

| Documents        |       | 퉬 dspba_sil_pcie                    | 2017/2/22 11:32 | File folder           |          |   |   |   |

| J Music          |       | 퉬 s5_ref                            | 2017/2/22 11:32 | File folder           |          |   |   |   |

| Pictures         |       |                                     |                 |                       |          |   |   |   |

| Videos           | Ŧ     |                                     |                 |                       |          |   |   |   |

Figure 2-2 DE5a-Net OpenCL BSP Content

### **2.2 OpenCL License Installation**

An OpenCL license is required for Intel FPGA OpenCL SDK to compile any OpenCL projects successfully. Developers can purchase the OpenCL license from either Altera or Terasic. Assuming that developers have obtained a license file with the filename "license.dat", and it is saved in the local disk with the file path such as "c:\license.dat". The license can then be set up by creating an environment variable **LM\_LICENSE\_FILE**, and set its value as "c:\license.dat". Note that this environment value needs to correspond to the actual "license.dat" file location.

Now, here are the procedures to create the required **LM\_LICENSE\_FILE** environment variable on Windows 7:

- 1. Open the Start Menu and right click on **Computer**. Select **Properties**.

- 2. Select Advanced system settings.

- 3. In the Advanced tab, select Environment Variables.

- 4. Select New.

- In the popup New User Variable dialog as shown in Figure 2-3, type "LM\_LIC ENSE\_FILE" in the Variable name edit box and type "c:\license.dat" in the Vari able value edit box.

| Edit User Variable | X               |

|--------------------|-----------------|

| Variable name:     | LM_LICENSE_FILE |

| Variable value:    | c:\icense.dat   |

|                    | OK Cancel       |

Figure 2-3 Setup LM\_LICENSE\_FILE Environment Variable

### 2.3 Configure

For Intel FPGA OpenCL SDK to be able to find the kit location of DE5a-Net correctly, developers need to create an environment variable **AOCL\_BOARD\_PACKAGE\_ROOT**, and set its value as:

$``\% ALTERAOCLSDKROOT\% \ board \ de5a_net_e1''$

Also, append "%AOCL\_BOARD\_PACKAGE\_ROOT%\windows64\bin" and "%ALTERAO CLSDKROOT%\bin" and "%ALTERAOCLSDKROOT%\windows64\bin" and "C:\intelFP GA\_pro\16.1\qsys\bin" into the PATH environment variable so the OpenCL SDK can find the binary file provided by DE5a-Net BSP.

Here are the procedures to create the required **AOCL\_BOARD\_PACKAGE\_ROOT** environment variable on Windows 7:

- 1. Open the Start Menu and right click on **Computer**. Select **Properties**.

- 2. Select Advanced system settings.

- 3. In the Advanced tab, select Environment Variables.

- 4. Select New.

- 5. In the popup New User Variable dialog as shown in Figure 2-4, type

"AOCL\_BOARD\_PACKAGE\_ROOT" in the Variable name edit box and type "%ALTERAOCLSDKROOT%\board\de5a\_net\_e1" in the Variable value edit box.

| Edit User Variable | 23                                      |

|--------------------|-----------------------------------------|

| Variable name:     | AOCL BOARD PACKAGE ROOT                 |

| Variable value:    | ntelFPGA_pro\16.1\hld\board\de5a_net_e1 |

|                    | OK Cancel                               |

Figure 2-4 Setup AOCL\_BOARD\_PACKAGE\_ROOT Environment Variable

Here are the procedures to add "%AOCL\_BOARD\_PACKAGE\_ROOT%\windows64\bin" and "%ALTERAOCLSDKROOT%\bin" and "%ALTERAOCLSDKROOT%\windows64\bin" and "C:\intelFPGA\_pro\16.1\qsys\bin" into the PATH environment variable on Windows 7:

- 1. Open the Start Menu and right click on **Computer**. Select **Properties**.

- 2. Select Advanced system settings.

- 3. In the Advanced tab, select Environment Variables.

- 4. In the Environment Variables window (as shown below), highlight the **PATH** variable in the Systems Variable section and click the **Edit** button as shown in Figure 2-5.

- In the Edit dialog, Append "%AOCL\_BOARD\_PACKAGE\_ROOT%\windows64\bin; %ALTERAOCLSDKROOT%\bin; %ALTERAOCLSDKROOT%\windows64\bin; C:\intelFPGA\_pro\16.1\qsys\bin" into the Variable value edit box. Note, each different directory should be separated with a semicolon as shown in Figure 2-6.

| Variable                                           | Value                                           |

|----------------------------------------------------|-------------------------------------------------|

| PATH                                               | C:\intelFPGA_pro\16.1\hld\bin;C:\intelF         |

| QSYS_ROOTDIR                                       | C:\intelFPGA_pro\16.1\quartus\sopc_b            |

| QUARTUS_ROO                                        |                                                 |

| SOPC_KIT_NIOS2                                     | C:\intelFPGA_pro\16.1\nios2eds                  |

|                                                    |                                                 |

|                                                    | New Edit Delete                                 |

|                                                    | New Edit Delete                                 |

| vstem variables                                    | New Edit Delete                                 |

| ystem variables                                    |                                                 |

| ystem variables<br>Variable                        | New Edit Delete                                 |

| -                                                  |                                                 |

| Variable                                           | Value<br>C:\Windows\system32\cmd.exe            |

| Variable<br>ComSpec                                | Value<br>C:\Windows\system32\cmd.exe<br>NO      |

| Variable<br>ComSpec<br>FP_NO_HOST_C                | Value<br>C:\Windows\system32\cmd.exe<br>NO      |

| Variable<br>ComSpec<br>FP_NO_HOST_C<br>NUMBER_OF_P | Value<br>C:\Windows\system32\cmd.exe<br>NO<br>4 |

Figure 2-5 Select "Path" and click "Edit" bottom

| Edit User Variable | 22                                 |

|--------------------|------------------------------------|

| Variable name:     | PATH                               |

| Variable value:    | 1;%ALTERAOCLSDKROOT%\windows64\bin |

|                    | OK Cancel                          |

Figure 2-6 Edit PATH environment variable

6. In Command Prompt window, type "**aocl install**" to install PCI Express driver. Note that users need to have administrator privileges to install the driver.

### 2.4 Board Setup

Before testing OpenCL on DE5a-Net, please follow the below procedures to set up DE5a-Net board on your PC as shown in Figure 2-7.

- 1. Make sure your PC is powered off.

- 2. Insert DE5a-Net board into PCI Express x8 or x16 slot.

- 3. Connect PC's 12V PCI Express 6-pin power source to the DE5a-Net

- 4. Connect PC's USB port to DE5a-Net mini USB port using an USB cable.

Note, the usb cable can be removed later if OpenCL code had been programming to the startup configuration flash of DE5a-Net by '**aocl flash** 'command.

Figure 2-7 Setup DE5a-Net board on PC

### **2.5 OpenCL Environment Verify and Flash CvP**

This section will show how to make sure the OpenCL environment is setup correctly. Firstly, please open **Command Prompt** windows by click Windows **Start** button, clicking **All Programs**, clicking **Accessories**, and then click **Command Prompt**.

### ■ Target Board

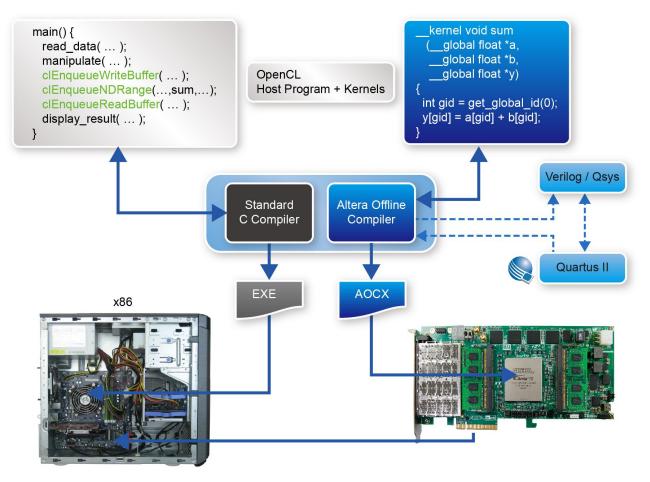

In Command Prompt window, type "**aoc --list-boards**" command, and make sure "**de5a\_net\_e1**" is listed in **Board list** as shown in **Figure 2-8**.

Figure 2-8 'de5a\_net\_e1' is listed in Board list

### ■ Test 'aocl flash' Command

In Command Prompt window, type "cd C: $intelFPGA_pro{16.1}hld\board\de5a_net_e1\tests\hell o_world\bin" to go to hello world OpenCL project folder.$

Then type "**aocl flash aclde5a\_net0 hello\_world.aocx**" to write **hello\_world.aocx** OpenCL image onto the startup configuration flash of DE5a-Net. Before flash programming, the programmer will ask users which startup configuration image area will be used as shown in **Figure 2-9**. This is because DE5a-Net provides two startup configuration image areas, called as Factory Image and User Image. We recommend users to key in '1' to select User Image area.

| Administrator: C:\Windows\system32\cmd.exe - aocl_flash aclde5a_net0 hello_world.aocx                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C:\intelFPGA_pro\16.1\hld\board\de5a_net_e1\tests\hello_world\bin>"C:/intelFPGA_<br>pro/16.1/quartus"\bin64\perl\bin\perl "C:\intelFPGA_pro\16.1\hld\board\de5a_net_<br>e1"\windows64\libexec\flash.pl aclde5a_net0 C:\Users\ADMINI~1\AppData\Local\Temp<br>/1516Commandpm541_1489997970_0_fpga_temp.bin<br>==================================== |

| I<br>Flash Programming                                                                                                                                                                                                                                                                                                                           |

| Info: ************************************                                                                                                                                                                                                                                                                                                       |

| Info: Version 16.1.0 Build 196 10/24/2016 SJ Pro Edition<br>Info: Copyright (C) 2016 Intel Corporation. All rights reserved.                                                                                                                                                                                                                     |

| Info: Your use of Intel Corporation's design tools, logic functions<br>Info: and other software and tools, and its AMPP partner logic                                                                                                                                                                                                            |

| Info: functions, and any output files from any of the foregoing                                                                                                                                                                                                                                                                                  |

| Info: (including device programming or simulation files), and any<br>Info: associated documentation or information are expressly subject                                                                                                                                                                                                         |

| Info: to the terms and conditions of the Intel Program License<br>Info: Subscription Agreement, the Intel Quartus Prime License Agreement,<br>Info: the Intel MegaCore Function License Agreement, or other                                                                                                                                      |

#### **Figure 2-9 Select Flash Page**

After users select desired flash area, it will take about 20 minutes for flash programming. **Figure 2-10** is the screen shot when flash programming is done successfully.

| E80000                                                                                                                                                                   |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Info (209005): Programming status: programming flash memory at byte address 0x0F<br>F90000                                                                               |  |  |  |  |

| Info (209005): Programming status: programming flash memory at byte address 0x0F                                                                                         |  |  |  |  |

| FA0000<br>Info (209005): Programming status: programming flash memory at byte address 0x0F                                                                               |  |  |  |  |

| FB0000<br>Info (209005): Programming status: programming flash memory at byte address 0x0F                                                                               |  |  |  |  |

| FC0000<br><u>Info (</u> 209005): Programming status: programming flash memory at byte address 0x0F                                                                       |  |  |  |  |

| FD0000<br>Info (209005): Programming status: programming flash memory at byte address 0x0F                                                                               |  |  |  |  |

| FE0000<br>Info (209005): Programming status: programming flash memory at byte address 0x0F                                                                               |  |  |  |  |

| FF0000<br>Info (209011): Successfully performed operation(s)                                                                                                             |  |  |  |  |

| Info (209061): Ended Programmer operation at Mon Nov 10 18:07:25 2016<br>Info: Quartus II 64-Bit Programmer was successful. 0 errors, 0 warnings                         |  |  |  |  |

| Info: Yuartus II 64-Bit Programmer was successful. 0 errors, 0 warnings<br>Info: Peak virtual memory: 2551 megabytes<br>Info: Processing ended: Mon Nov 10 18:07:25 2016 |  |  |  |  |

| Info: Elapsed time: 00:38:52<br>Info: Total CPU time (on all processors): 00:00:34                                                                                       |  |  |  |  |

| C:\intelFPGA_pro\16.1\hld\board\de5a_net_e1\tests\hello_world\bin>                                                                                                       |  |  |  |  |

|                                                                                                                                                                          |  |  |  |  |

#### Figure 2-10 aocl flash aclde5a\_net\_e10 hello\_world.aocx" successfully

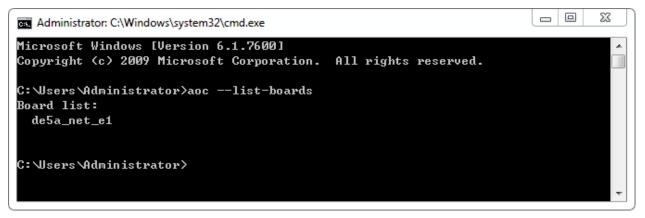

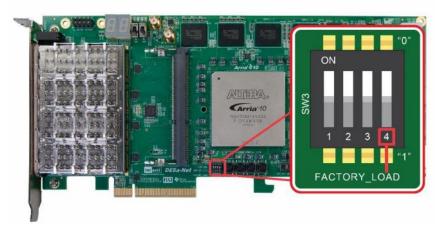

To make sure a correct image is used when FPGA boots up, please make sure the dip switch SW3.4 on DE5a-Net is changed to the correct location. If a User Image area is selected, the dip switch SW3.4 on the DE5a-Net should be moved to **Up** position as shown in **Figure 2-.**

Figure 2-11 Set SW3.4 to Up Position (User Image Page)

After flash programming is done successfully and SW3.4 is set to correct position, developers can power off PC and DE5a-Net board, then turn it back on.

### ■ Test 'aocl diagnose' Command

The diagnose utility in the Arria 10 DE5a-Net board reports device information and identifies issues. The diagnose utility first verifies the installation of the kernel driver and returns the overall information of all the devices installed in a host machine.

In Command Prompt window, type "**aocl diagnose**" to check if the initialization completed successfully. If successful, the programming message displays "**DIAGNOSTIC\_PASSED**" as shown in Figure 2-12.

| Administrator: C:\Windows\system32\cmd.exe                                                                                                               |         | 23    |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|--|--|--|

| Microsoft Windows [Version 6.1.7600]<br>Copyright <c> 2009 Microsoft Corporation. All rights reserved.</c>                                               |         | III > |  |  |  |

| C:\Users\Administrator>aocl diagnose<br>aocl diagnose: Running diagnose from C:\intelFPGA_pro\16.1\hld\board\de5a_net_e1<br>/windows64/libexec           |         |       |  |  |  |

| acl0<br>Vendor: Terasic                                                                                                                                  |         |       |  |  |  |

| Phys Dev Name Status Information                                                                                                                         |         |       |  |  |  |

| aclde5a_net0 Passed Arria 10 Reference Platform (aclde5a_net0)<br>PCIe dev_id = 2494, bus:slot.func = 01:00.00,<br>FPGA temperature = 35.3672 degrees C. | Gen3 x8 |       |  |  |  |

| DIAGNOSTIC_PASSED                                                                                                                                        |         |       |  |  |  |

| C:\Users\Administrator>                                                                                                                                  |         | 4     |  |  |  |

Figure 2-12 "aocl diagnose" messages

**Note:** For DE5a-Net to negotiate with the host PC at Gen 3 as the link speed, it is strongly recommended that users set the PCIe speed at Gen 3 in the BIOS on the host PC. If your PC support PCIe Gen3x8, but it gets incorrect detected information, you can modify the PCIe settings in the BIOS, and reboot.

#### ■ Test 'aocl program' Command

Check whether the **hello\_world** OpenCL image, which is CvP enabled, configures the FPGA successfully. In Command Prompt window, type "cd C:\intelFPGA\_pro\16.1\hld\board\ de5a\_net\_e1\tests\hello\_world\bin" to go to **hello\_world\bin** project folder, then type "**aocl program aclde5a\_net0 hello\_world.aocx**" to configure the FPGA with **hello\_world.aocx** OpenCL image. If the programming message displays "Program succeed" as shown in **Figure 2-12**, it means the **hello\_world** OpenCL image is programmed into the flash correctly and CvP works well.

23 Administrator: C:\Windows\system32\cmd.exe Microsoft Windows [Version 6.1.7600] . Copyright (c) 2009 Microsoft Corporation. All rights reserved. C:\Users\Administrator>cd C:\intelFPGA\_pro\16.1\hld\board\de5a\_net\_e1\tests\hell o\_world∖bin C:\intelFPGA\_pro\16.1\hld\board\de5a\_net\_e1\tests\hello\_world\bin>aocl program a clde5a\_net0 hello\_world.aocx aocl program: Running program from C:\intelFPGA\_pro\16.1\hld\board\de5a\_net\_e1/w indows64/libexec Programming device: de5a\_net\_e1 : Arria 10 Reference Platform (aclde5a\_net0) Reprogramming device with handle 1 Program succeed. C:\intelFPGA\_pro\16.1\hld\board\de5a\_net\_e1\tests\hello\_world\bin>

Figure 2-12 "aocl program aclde5a\_net0 hello\_world.aocx" use CvP

### **2.6 Compile and Test OpenCL Project**

This section will show how to compile and test OpenCL kernel and OpenCL Host Program for the vector\_add project. Developers can use the same procedures to compile and test other OpenCL examples for DE5a-Net.

### **Compile OpenCL Kernel**

The utility **aoc** (Altera SDK for OpenCL Kernel Compiler) is used to compile OpenCL ker nel. In Command Prompt window,type "cd C:\intelFPGA\_pro\16.1\hld\board\de5a\_net\_e1\tests\ vector\_add" to go to **vector\_add** project folder, then type "**aoc device\vector\_add.cl -o bin**\ **vector\_add.aocx --board de5a\_net\_e1**" to compile the OpenCL kernel. It will take about o ne hour for compiling. When the compilation process is finished, OpenCL image file vector \_add.aocx is generated. Figure 2-13 is the screenshot when OpenCL kernel is compiled su ccessfully. For required parameters to compile vector\_add.cl, please refer to the README.tx t that is in the same folder as the vector\_add.cl. For detailed usage of aoc, please refer to the Altera SDK for OpenCL Programming Guide:

https://www.altera.com/en\_US/pdfs/literature/hb/opencl-sdk/aocl\_programming\_guide.pdf

23 Administrator: C:\Windows\system32\cmd.exe - aoc device\vector\_add.cl -o bin\vector\_add.aocx -... Microsoft Windows [Version 6.1.7600] ٨ Copyright (c) 2009 Microsoft Corporation. All rights reserved. Ξ C:\Users\Administrator>cd C:\intelFPGA\_pro\16.1\hld\board\de5a\_net\_e1\tests\vect or\_add C:\intelFPGA\_pro\16.1\hld\board\de5a\_net\_e1\tests\vector\_add>aoc device\vector\_a dd.cl -o bin\wector\_add.aocx --board de5a\_net\_e1 c:/intelFPGA\_pro/16.1/hld/board/de5a\_net\_e1/tests/vector\_add/device/vector\_add.c 1:23:48: warning: declaring kernel argument with no 'restrict' may lead to low k ernel performance \_kernel void vector\_add(\_\_global const float \*x, c:/intelFPGA\_pro/16.1/hld/board/de5a\_net\_e1/tests/vector\_add/device/vector\_add.c 1:24:48: warning: declaring kernel argument with no 'restrict' may lead to low k ernel performance \_\_global const float \*y, 2 warnings generated.

Figure 2-13 "aoc vector\_add.cl" OpenCL kernel compile

### **Compile Host Program**

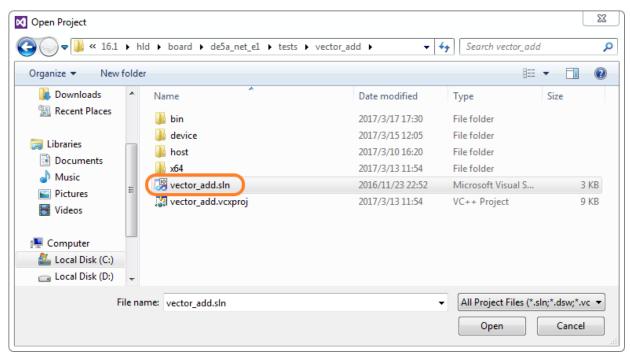

Visual Studio C/C++ 2012 is used to compile the Host Program. Launch Visual Studio, and select menu item "FILE $\rightarrow$ Open Project...". In the Open Project dialog, go to the folder "C:\intelFPGA\_pro\16.1\hld\board\de5a\_net\_e1\tests\vector\_add", and select "vector\_add.sln" as shown Figure 2-14.

#### Figure 2-14 Open vector\_add.sln Host Program

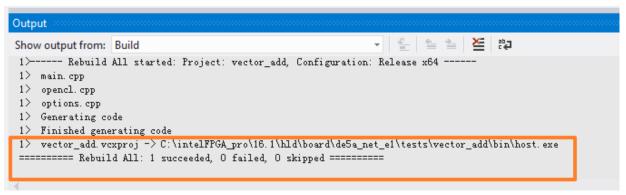

After vector\_add Host Program project is opened successfully, in Visual Studio IDE select menu item "BUILD $\rightarrow$ Build Solution" to build host program. When build is successfully, you will see successful message as show in Figure 2-15. The execute file is generate in:

$\label{eq:control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_control_optimal_co$

Figure 2-15 Message for vector\_add Host Program build successfully

### ■ Test vector\_add project

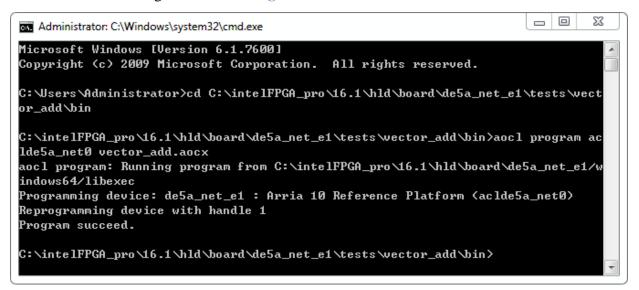

Firstly, use the compiled OpenCL image file vector\_add.aocx to configure the FPGA. In Command Prompt window, type "cd C:\intelFPGA\_pro\16.1\hld\board\de5a\_net\_e1\tests\vector\_add\bin" to go to **vector\_add\bin** project folder, then type "**aocl program aclde5a\_net0 vector\_add.aocx**" to configure FPGA with the OpenCL Image vector\_add.aocx. If configuration is successfully, you will see the successful message as shown in Figure 2-16.

Figure 2-16 "aocl program aclde5a\_net0 vector\_add.aocx" configured successfully

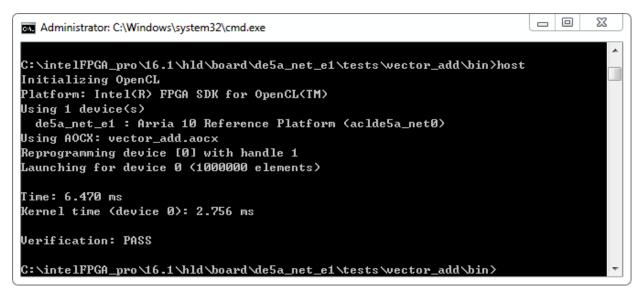

In Command Prompt window, execute "**host.exe**". **Figure 2-17** is the screen shot when the test is successful.

## Chapter 3

**OpenCL** for Linux

This chapter describe how to setup DE5a-Net OpenCL development environment on 64-bit Linux (Red Hat Enterprise Linux 6.5/CentOS 7.0 are recommended), and how to compile and test the OpenCL examples for DE5a-Net. For more details about Altera OpenCL , please refer to Altera SDK for OpenCL Getting Started document:

https://www.altera.com/en\_US/pdfs/literature/hb/opencl-sdk/aocl\_getting\_started.pdf

### **3.1 Software Installation**

This section describes how to download and install the required software for OpenCL.

### ■ Altera Quartus II and OpenCL

Intel Quartus Prime Pro Edition 16.1 and Intel FPGA SDK for OpenCL 16.1 can be download from the web site:

#### http://dl.altera.com/opencl/16.1/?edition=standard

For Quartus II installation, please make sure that the Arria 10 device is included.

open the link and select the Linux SDK as Figure 3-1 shows.

#### Download Center

Get the complete suite of Intel® design tools

|                       | 😗 myAltera Account Help 🛛 🗗 Terms and Con                                                                                      |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Design Software       |                                                                                                                                |

| Embedded Software     | Intel FPGA SDK for OpenCL™                                                                                                     |

| Archives              | Release date: November, 2016                                                                                                   |

| Licensing             | Latest Release: v16.1                                                                                                          |

| Programming Software  | Select release: 16.1                                                                                                           |

| Drivers               |                                                                                                                                |

| Board System Design   | Download Method 👩 🖲 Akamai DLM3 Download Manager 🕜 🛛 🔍 Direct Download                                                         |

| Board Layout and Test |                                                                                                                                |

| Legacy Software       | Windows SDK Linux SDK RTE Updates                                                                                              |

|                       | Download and install instructions:                                                                                             |

|                       | Read Intel FPGA SDK for OpenCL Getting Started Guide                                                                           |

|                       | Intel FPGA SDK for OpenCL (includes Quartus Prime software and devices)<br>Size: 20.3 GB MD5: B3C9078830DD995A17F0B07C5DF089EE |

|                       | Download                                                                                                                       |

#### Figure 3-1 Linux SDK table

In the software download selection form, choose **Software and devices** as **Figure 3-2** show.

| Intel FPGA SDK for                                    | OpenCL™                                                                 |        |

|-------------------------------------------------------|-------------------------------------------------------------------------|--------|

| Release date: November, 2016<br>Latest Release: v16.1 | 1. Quartus Prime Standard Edition                                       |        |

| Select release: 16.1 🔻                                | 2. Quartus Prime Pro Edition<br>3. Intel FPGA SDK for OpenCL            |        |

| Download Method 👔 🖲 Akamai [                          | 4. Arria 10 Part 1<br>5. Arria 10 Part 2                                | wnload |

| Windows SDK Linux SDI                                 | 6. Arria 10 Part 3<br>7. Arria V                                        |        |

| Download and install inst                             | 8. Cyclone V<br>9. Stratix V                                            |        |

| Read Intel FPGA SDK for Ope                           | her octang otarten onne                                                 | -      |

|                                                       | <b>CL (includes Quartus Prime softwa</b><br>178830DD995A17F0B07C5DF089E |        |

| Download                                              |                                                                         |        |

#### Figure 3-2 software and devices download

Quartus II software uses the built-in USB-Blaster II drivers on Linux to access USB-Blaster II download cable on DE5a-Net. but after installed the Quartus II software with built-in drivers, User need to change the port permission for USB-Blaster II via issuing

'gedit /etc/udev/rules.d/51-usbblaster.rules'

to create and add the following lines to the /etc/udev/rules.d/51-usbblaster.rules file.

```

# USB-Blaster

BUS=="usb", SYSFS{idVendor}=="09fb", SYSFS{idProduct}=="6001", MODE="0666"

BUS=="usb", SYSFS{idVendor}=="09fb", SYSFS{idProduct}=="6002", MODE="0666"

BUS=="usb", SYSFS{idVendor}=="09fb", SYSFS{idProduct}=="6003", MODE="0666"

# USB-Blaster II

BUS=="usb", SYSFS{idVendor}=="09fb", SYSFS{idProduct}=="6010", MODE="0666"

BUS=="usb", SYSFS{idVendor}=="09fb", SYSFS{idProduct}=="6810", MODE="0666"

```

Note: You must have system administration (root) privileges to configure the USB-Blaster download cable drivers.

### **GNU development tools**

GNU development tools such as gcc(include g++) and make are required to build the driver and application under Linux. User can issue 'yum install gcc ccompat-gcc-48-c++ make' command to download and install them and their dependencies via internet.

Note: To install the SDK on Linux, you must install it in a directory that you own (that is, a directory that is not a system directory). You must also have sudo or root privileges.

### ■ DE5a-Net openCL BSP (Board Support Package)

After Quartus II and OpenCL SDK are installed, please download the DE5ANET\_E1\_Open CL\_BSP\_16.1.tar.gz DE5a-Net linux BSP for Altera OpenCL 16.1 from the web:

### http://de5a-net.terasic.com/cd

Then, decompress DE5ANET\_E1\_OpenCL\_BSP\_16.1.tar.gz to the "**de5a\_net\_e1**" folder under the folder "/root/intelFPGA\_pro/16.1/hld/board", where assumed Quartus II is installed on the folder "/root/ intelFPGA\_pro/16.1", as shown in **Figure 3-3**.

Figure 3-3 DE5a-Net OpenCL BSP Content

### **3.2 OpenCL License Installation**

An OpenCL license is required to compile the OpenCL projects for Altera OpenCL SDK. Developers can purchase the OpenCL license from either Altera or Terasic. Assuming that developers have obtained a license file with the filename "license.dat", and it is saved in the local disk with the file path such as "/root/intelFPGA\_pro/16.1/hld/license.dat". The license can then be set up by creating an environment variable LM\_LICENSE\_FILE, and set its value as "/root/ intelFPGA\_pro /16.1/hld/license.dat".

Note that this environment value needs to correspond to the actual "license.dat" file location.

The next chapter will describe the license environment setting up.

### **3.3 Configure**

DE5a-Net OpenCL

If you install the ALTERA FPGA development software and OpenCL SDK on a system that does not contain any .cshrc or Bash Resource file (.bashrc) in your directory, you must set the ALTERAOCLSDKROOT and PATH environment variables manually. And for Altera OpenCL SDK able to find the kit location of DE5a-Net correctly, the developers need to create an

22

environment variable for the DE5a-Net board AOCL\_BOARD\_PACKAGE\_ROOT, and set its value as:

"\$ALTERAOCLSDKROOT"/board/de5a\_net\_e1"

Alternatively, you can edit the "/etc/profile" **profile** file, and append the environment variables to it. To do this type "*gedit /etc/profile*" *command on Linux Terminal* to open the **profile** file by the **gedit** editor tool, and append the following setting to the **profile** file. Then, save the file and type "*source /etc/profile*" command in Linux Terminal to make the settings make effect.

export QUARTUS\_ROOTDIR=/root/intelFPGA\_pro/16.1/quartus export ALTERAOCLSDKROOT=/root/ intelFPGA\_pro/16.1/hld export AOCL\_BOARD\_PACKAGE\_ROOT=\$ALTERAOCLSDKROOT"/board/de5a\_net\_e1 export PATH=\$PATH:\$QUARTUS\_ROOTDIR/bin:\$ALTERAOCLSDKROOT/linux64/bin:\$ALTERAOCLSDKR OOT/bin:\$ALTERAOCLSDKROOT/host/linux64/bin:/root/intelFPGA\_pro/16.1/qsys/bin export LD\_LIBRARY\_PATH=\$AOCL\_BOARD\_PACKAGE\_ROOT/linux64/lib:\$ALTERAOCLSDKROOT /host/linux64/lib:\$AOCL\_BOARD\_PACKAGE\_ROOT/tests/extlibs/lib export QUARTUS\_64BIT=1 export LM\_LICENSE\_FILE=/root/ intelFPGA\_pro/16.1/hld/license.dat

### 3.4 Board Setup

Before testing OpenCL on DE5a-Net, please following the below procedure to setup DE5a-Net board on your PC as shown in Figure 3-4.

- 1. Make sure your PC is power off.

- 2. Insert DE5a-Net board into PCI Express x8 or x16 slot.

- 3. Connect PC's 12V PCI Express 6-pin power to the DE5a-Net source (if there's not, ignore this step)

- 4. Connector PC's USB port to DE5a-Net mini USB port using an USB cable.

Note, the usb cable can be removed later if any one of OpenCL code had been programming to the startup configuration flash of DE5a-Net by '**aocl flash**' command.

Figure 3-4 Setup DE5a-Net board on PC

### **3.5 OpenCL Environment Verify and Flash CvP**

This section will show how to make sure the OpenCL environment is setup correctly.

Firstly, please open the Linux system **terminal** window by right click the Mouse on system desktop, then clicking on **Open Terminal**.

### Target Board

In the Linux terminal, type "*aoc --list-boards*" command, and make sure "**de5a\_net\_e1**" is listed in **Board list** as shown in **Figure 3-5**.

| root@localhost:~/Desktop                                               | - | × |

|------------------------------------------------------------------------|---|---|

| File Edit View Search Terminal Help                                    |   |   |

| [root@localhost Desktop]# aoclist-boards<br>Board list:<br>de5a_net_e1 |   |   |

| [root@localhost Desktop]#                                              |   |   |

#### Figure 3-5 'de5a\_net\_e1' is listed in Board list

Then type "aocl install" to load the PCIe driver for the DE5a-Net as shown in Figure 3-6.

```

root@localhost:~/intelFPGA_pro/16.1/hld/board

×

File Edit View Search Terminal Help

[root@localhost board]# aocl install

aocl install: Running install from /root/intelFPGA pro/16.1/hld/board/de5a net e

1/linux64/libexec

Using kernel source files from /lib/modules/3.10.0-327.22.2.el7.x86_64/build

Building driver for BSP with name de5a net e1

make: Entering directory `/usr/src/kernels/3.10.0-327.22.2.el7.x86 64'

/tmp/opencl driver r0tngI/aclpci queue.o

CC [M]

CC [M]

/tmp/opencl driver r0tngI/aclpci.o

/tmp/opencl driver r0tngI/aclpci fileio.o

CC [M]

CC [M]

/tmp/opencl driver r0tngI/aclpci dma.o

CC [M]

/tmp/opencl driver r0tngI/aclpci pr.o

/tmp/opencl_driver_r0tngI/aclpci_cmd.o

CC [M]

/tmp/opencl_driver_r0tngI/aclpci_de5a_net_e1_drv.o

LD [M]

Building modules, stage 2.

MODPOST 1 modules

/tmp/opencl driver r0tngI/aclpci de5a net e1 drv.mod.o

CC

LD [M] /tmp/opencl driver r0tngI/aclpci de5a net e1 drv.ko

make: Leaving directory `/usr/src/kernels/3.10.0-327.22.2.el7.x86 64'

[root@localhost board]# 📕

```

#### Figure 3-6 driver installation

Note: if user don't using the recommended Linux system or different version, recompile the driver is needed. You can compile it by typing *"cd root/intelFPGA\_pro/16.1/hld/board/de5a\_net\_e1/ linux64/driver"* (there are source code, makefile and readme.txt)to *locate at the* driver source code directory and type *"./make\_all"* to compile and generate the new driver. Before that, user need to install the kernel related development package matched the current kernel (**kernel-devel** package) via issuing *'yum install kernel-devel*' command.

### Test 'aocl flash' Command

In the terminal, type "*cd /root/intelFPGA\_pro/16.1/hld/board/de5a\_net\_e1/tests/hello\_world/bin*" to go to hello world OpenCL project folder, then type "*aocl flash aclde5a\_net\_e10 hello\_world.aocx*" to program **hello\_world.aocx** OpenCL image onto the startup configuration flash of DE5a-Net.

Before flash programming, the programmer will ask users which startup configuration image area will be used as shown in **Figure 3-7**. This is because DE5a-Net provides two startup configuration image areas, called as Factory Image and User Image. Typing '1' to select User Image area is recommended.

| root@localhost:~/intelFPGA_pro/16.1/hld/board/de5a_net_e1/tests/hello_world/bin _ 🛛 🗙                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| File Edit View Search Terminal Help                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| [root@localhost bin]# aocl flash aclde5a_net_e10 hello_world.aocx<br>aocl flash: Running flash from /root/intelFPGA_pro/16.1/hld/board/de5a_net_e1/li<br>nux64/libexec<br>6M                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| <pre>====================================</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Flash Programming<br>Info: ************************************                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Info: Running Quartus Prime Convert_programming_file<br>Info: Version 16.1.0 Build 196 10/24/2016 SJ Pro Edition<br>Info: Copyright (C) 2016 Intel Corporation. All rights reserved.<br>Info: Your use of Intel Corporation's design tools, logic functions                                                                                                                                                                                                                                  |  |  |  |  |

| Info: and other software and tools, and its AMPP partner logic<br>Info: functions, and any output files from any of the foregoing<br>Info: (including device programming or simulation files), and any<br>Info: associated documentation or information are expressly subject<br>Info: to the terms and conditions of the Intel Program License<br>Info: Subscription Agreement, the Intel Quartus Prime License Agreement,<br>Info: the Intel MegaCore Function License Agreement, or other |  |  |  |  |

**Figure 3-7 Select Flash Page**

After selecting the desired flash area, it will take about 20 minutes for flash programming. **Figure 3-8** is the screen shot when flash programming is done successfully.

```

Info (209005): Programming status: programming flash memory at byte address 0x0F

FA0000

Info (209005): Programming status: programming flash memory at byte address 0x0F

FB0000

Info (209005): Programming status: programming flash memory at byte address 0x0F

FC0000

Info (209005): Programming status: programming flash memory at byte address 0x0F

FD0000

Info (209005): Programming status: programming flash memory at byte address 0x0F

FE0000

Info (209005): Programming status: programming flash memory at byte address 0x0F

FF0000

Info (209011): Successfully performed operation(s)

Info (209061): Ended Programmer operation at Fri Nov 7 16:38:39 2016

Info: Quartus II 64-Bit Programmer was successful. 0 errors, 0 warnings

Info: Peak virtual memory: 2681 megabytes

Info: Processing ended: Fri Nov 7 16:38:39 2016

Info: Elapsed time: 00:11:22

Info: Total CPU time (on all processors): 00:02:19

[root@localhost bin]# 🗌

```

#### Figure 3-8 'aocl flash aclde5a\_net\_e10 hello\_world.aocx" successfully

To make sure correct image is used when FPGA boot, please make sure the dip switch SW3.4 on DE5a-Net is located at correct location. If User Image area is selected, the dip switch SW3.4 on the DE5a-Net should be move to **up** position as shown in **Figure 3-9**.

Figure 3-9 Set SW3.4 to Left Position (User Image Page)

After flash programming is done successfully and SW3.4 is set to correct position, developers can power off PC and DE5a-Net board, then turn it back on.

### Test 'aocl diagnose' Command

The diagnose utility in the Arria 10 DE5a-Net board reports device information and identifies issues. The diagnose utility first verifies the installation of the kernel driver and returns the overall information of all the devices installed in a host machine.

In the Linux terminal, type "**aocl diagnose**" to check if the initialization completed successfully. If successful, the programming message displays "**DIAGNOSTIC\_PASSED**" as shown in **Figure 3-10**.

|                                                          | root@localhost:~/Desktop                                                                                                              | -     |      | ×  |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------|------|----|

| File Edit View Search Ter                                | minal Help                                                                                                                            |       |      |    |

| [root@localhost Desktop]<br>aocl diagnose: Running d<br> | # aocl diagnose<br>liagnose from /root/intelFPGA_pro/16.1/hld/boar                                                                    | d/de  | 5a_n | et |

| Vendor: Terasic                                          | - acl0                                                                                                                                |       |      |    |

| Phys Dev Name Status                                     | Information                                                                                                                           |       |      |    |

| Р                                                        | Arria 10 Reference Platform (aclde5a_net_e10)<br>CIe dev_id = 2494, bus:slot.func = 01:00.00, G<br>PGA temperature = 36.75 degrees C. | en3 : | x8   |    |

| DIAGNOSTIC_PASSED                                        |                                                                                                                                       |       |      |    |

| [root@localhost Desktop]                                 | #                                                                                                                                     |       |      |    |

DE5a-Net OpenCL

www.terasic.com March 29, 2017 **Note:** For DE5a-Net to negotiate with the host PC at Gen 3 as the link speed, it is strongly recommended that users set the PCIe speed at Gen 3 in the BIOS on the host PC. If your PC support PCIe Gen3x8, but detected is incorrect, you can modify the PCIe settings in the BIOS, and reboot.

### ■ Test 'aocl program' Command

Check whether the hello\_world OpenCL image, which is CvP enabled, configures the FPGA successfully when DE5a-Net is power on. In the Linux terminal. type "cd /root/intelFPGA\_pro/16.1/hld/board/de5a\_net\_e1/tests/hello\_world/bin" to go to hello\_world project folder, then type "aocl program aclde5a net e10 hello world.aocx" to configure the FPGA with hello world.aocx OpenCL image. If the programming message displays "Program succeed" as shown in Figure 3-10, it means the hello\_world OpenCL image is programmed into the flash correctly and CvP works well.

root@localhost:~/intelFPGA\_pro/16.1/hld/board/de5a\_net\_e1/tests/hello\_world/bin \_ □ ×

File Edit View Search Terminal Help

[root@localhost bin]# aocl program aclde5a\_net\_e10 hello\_world.aocx

aocl program: Running program from /root/intelFPGA\_pro/16.1/hld/board/de5a\_net\_e

1/linux64/libexec

Programming device: de5a\_net\_e1 : Arria 10 Reference Platform (aclde5a\_net\_e10)

Reprogramming device [0] with handle 1

Program succeed.

[root@localhost bin]#

Figure 3-10 'aocl program aclde5a\_net0 hello\_world.aocx" use CvP

### **3.6 Compile and Test OpenCL Project**

This section will show how to compile and run the OpenCL kernel and OpenCL Host Program for the vector\_add example project. Developers can use the same procedures to compile and test other OpenCL examples (included in the kit) for DE5a-Net.

### Compile OpenCL Kernel

In the terminal, type "*cd /root/intelFPGA\_pro/16.1/hld/board/de5a\_net\_e1/tests/vector\_add*" to go to **vector\_add** project folder, then type "*aoc device/vector\_add.cl -o bin/vector\_add.aocx --board de5a\_net\_e1 --report*" to compile the OpenCL kernel. It will takes about one hour for compiling. After that, the OpenCL image file *vector\_add.*aocx is generated. Figure 3-11 is the screen shot when OpenCL kernel is compiled successfully. For required parameters to compile vector\_add.cl,

please refer to the README.txt that is in the same directory.

The utility **aoc** (Altera SDK for OpenCL Kernel Compiler) is used to compile OpenCL kernel. For detailed usage of **aoc**, please refer to the **Altera SDK for OpenCL Programming Guide**:

http://www.altera.com/literature/hb/opencl-sdk/aocl\_programming\_guide.pdf

| root@localhost:"/intelFPGA_pro/16.1/hld/board/de5a_net_e1/tests/vector_add _ 🛛 🗛 😽                                                                                                                                                                                |                                                                                                        |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| File Edit View Search Terminal Help                                                                                                                                                                                                                               |                                                                                                        |  |  |  |  |  |  |

| <pre>[root@localhost vector_add]# aoc device/v oard de5a_net_e1report aoc: Selected target board de5a_net_e1 /root/intelFPGA_pro/16.1/hld/board/de5a_r d.cl:23:48: warning: declaring kernel arg w kernel performancekernel void vector_add(global const f </pre> | net_el/tests/vector_add/device/vector_ad<br>gument with no 'restrict' may lead to lo<br>float *x,<br>^ |  |  |  |  |  |  |

| /root/intelFPGA_pro/16.1/hld/board/de5a_net_e1/tests/vector_add/device/vector_ad<br>d.cl:24:48: warning: declaring kernel argument with no 'restrict' may lead to lo<br>w kernel performance<br>global const float *y,                                            |                                                                                                        |  |  |  |  |  |  |

| 2 warnings generated.                                                                                                                                                                                                                                             |                                                                                                        |  |  |  |  |  |  |

| ++<br>; Estimated Resource Usage Summary ;<br>++                                                                                                                                                                                                                  |                                                                                                        |  |  |  |  |  |  |

| ; Resource                                                                                                                                                                                                                                                        | + Usage ;                                                                                              |  |  |  |  |  |  |

| ; Logic utilization<br>; ALUTs<br>; Dedicated logic registers<br>; Memory blocks<br>; DSP blocks<br>+                                                                                                                                                             | ; 19%<br>; 10%<br>; 10%<br>; 11%<br>; 5%                                                               |  |  |  |  |  |  |

Figure 3-11 'aoc vector\_add.cl" OpenCL kernel compile successfully

### **Compile Host Program**

In the terminal, type "*cd* /*root/intelFPGA\_pro/16.1/hld/board/de5a\_net\_e1/tests/vector\_add*" and then type "*make*" to compile the host program.

When build is successfully, you will see successful message as show in **Figure 3-12**. The execute file is generate in the same directory which named bin.

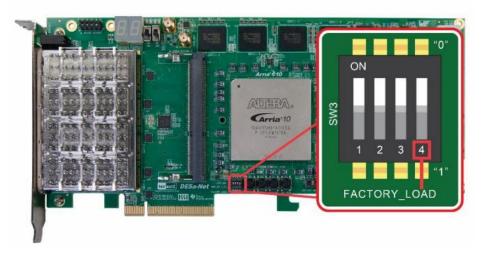

### Test vector\_add project

Firstly, In the terminal, type "*cd /root/intelFPGA\_pro/16.1/hld/board/de5a\_net\_e1/tests/vector\_add/bin*" to go to the **vector\_add** project folder, then type "*aocl program aclde5a\_net\_e10 vector\_add.aocx*" to configure FPGA with the OpenCL Image vector\_add.aocx.

Then, launch the compiled Host Program to start vector\_add execute file for test. In the terminal type "./host". Figure 3-13 shows the execution is successful.

```

root@localhost:~/intelFPGA_pro/16.1/hld/board/de5a_net_e1/tests/vector_add/bin

×

File Edit View Search Terminal Help

[root@localhost bin]# aocl program aclde5a net e10 vector add.aocx

aocl program: Running program from /root/intelFPGA pro/16.1/hld/board/de5a net e

1/linux64/libexec

Programming device: de5a net e1 : Arria 10 Reference Platform (aclde5a net e10)

Reprogramming device [0] with handle 1

Program succeed.

[root@localhost bin]# ./host

Initializing OpenCL

Platform: Intel(R) FPGA SDK for OpenCL(TM)

Using 1 device(s)

de5a_net_e1 : Arria 10 Reference Platform (aclde5a_net_e10)

Using AOCX: vector_add.aocx

Reprogramming device [0] with handle 1

Launching for device 0 (1000000 elements)

Time: 6.446 ms

Kernel time (device 0): 2.830 ms

Verification: PASS

[root@localhost bin]#

```